Hybrid Bonding: The Next Frontier in Semiconductor Interconnects

Revolutionizing Die-to-Die Connections with High-Speed, Low-Power, and Compact Solutions Despite Cost Challenges

3 Key Thrusts for Innovation in the semiconductor and AI domain

Interconnect Scaling with Hybrid Bonding:

Micrographs of advanced hybrid bonding techniques for chip interconnections.

The bonding interface at a microscopic scale, with annotations for dimensions (e.g., 3 μm, 1 μm) for the bonding interface, top pad, and bottom pad.

This innovation focuses on enabling more efficient and denser connections between chips.

Advanced Memory Integration:

A pyramid diagram illustrating the memory hierarchy and integration strategies.

At the base is SSD Storage, offering high capacity but lower speed and energy efficiency.

Progressing upwards: Persistent Memory, DRAM System Main Memory, HBM (High Bandwidth Memory), and SRAM Cache at the top for highest performance and energy efficiency.

The diagram highlights trends in memory development: higher capacity, lower cost towards the base, and increasing energy per bit towards the top.

System Expansion:

The right panel showcases a visual representation of the Cerebras WSE-2 chip, highlighting its massive scale:

2.6 Trillion Transistors

46,225 mm² of Silicon

This represents a leap in system-level scalability, emphasizing large-scale chip designs for high performance.

The innovations focus on enhancing system-level power and performance, modularity, scalability, and cost efficiency. These advancements are critical for next-generation computing systems.

Recently, particularly in cases where silicon interposers are used, a technology called "MicroBump," which features extremely small solder ball diameters, has been employed. However, even with this approach, the following issues remain:

Pitch Limitation: As long as bumps are used, the expansion of solder when subjected to temperature (and pressure) makes it extremely difficult to achieve a pitch (spacing between bumps) of less than 10 μm.

Electrical Resistance: Bumps are fundamentally composed of solder (recently, alloys of tin, copper, and silver are commonly used instead of lead, though the composition varies depending on the application). Because reliable connections are prioritized, bumps often exhibit higher electrical resistance.

Signal Routing: Since signals passing through bumps are essentially treated as exiting the chip, an output circuit (Fan Out) is required, even if it doesn’t involve a full PHY. This leads to increased power consumption during communication and a very slight increase in latency.

What is Hybrid Bonding?

Hybrid Bonding is a chip connection technology that differs from the mainstream Bump (solder bump) bonding used in packaging. Hybrid Bonding connects chips through a combination of metal (e.g., copper) and oxide bonding. Its primary advantage lies in reducing the bump pitch and contact spacing, which increases connection density within the same area. This, in turn, enables faster transmission speeds and reduces power consumption.

This method connects two dies (or a die and a package) directly without relying on bumps. However, at present, connecting dies to packages remains challenging, so this technique is primarily limited to 3D stacking of dies. Examples of Hybrid Bonding include TSMC's SoIC and Intel's Foveros Direct. The advantages of this method, which contrast with those of bump-based connections, are indispensable for achieving higher speeds and lower power consumption:

Improved Pitch: Since solder does not expand during bonding, achieving a pitch of less than 10 μm is entirely feasible.

Reduced Resistance: The direct contact between copper and copper minimizes excess resistance, thereby reducing power consumption and parasitic capacitance-induced latency.

Fan Out Minimization: Essentially, Fan Out is unnecessary (though minimal protection circuits are still included).

TSMC: Hybrid Bonding Applied to the New 3D Advanced Packaging Technology - SoIC

Amid the surge of demand driven by the AI revolution, the demand for CoWoS (Chip-on-Wafer-on-Substrate) capacity has skyrocketed, prompting TSMC to actively expand its CoWoS production capabilities. In addition to CoWoS, TSMC has another 3D advanced packaging technology: SoIC (System-on-Integrated-Chips).

SoIC is the industry's first high-density 3D chiplet stacking technology, enabling wafer-level bonding for advanced nodes at 10nm and below.

SoIC offers two stacking solutions: SoIC-P (Bumped) and SoIC-X (Bumpless).

SoIC-P is a micro-bump stacking solution designed for cost-sensitive applications such as mobile devices.

SoIC-X, on the other hand, employs Hybrid Bonding and is ideal for high-performance computing (HPC) and AI applications.

Intel: Advanced Packaging with Hybrid Bonding: Foveros Direct 3D

Foveros Direct 3D is an Intel technology that enables direct attach of one or more chiplets to an active base tile to create complex system modules. “Direct” attach is achieved by thermocompression bonding of copper vias on individual chiplets to those on a wafer or even direct bonding of entire wafers stacked atop each other.

The attachment can be “Face-to-Face” or “Face-to-Back” and can include chips or wafers from different source foundries, offering more flexibility in product architecture. The connection bandwidth is determined by the copper via pitch (and resulting density). The first generation of Foveros Direct 3D will use copper bonding at a pitch of 9um while the second generation will shrink the pitch to just 3um.

Hybrid Bonding Challenges

Defect Issues:

Images on the left illustrate different types of bonding issues:

Non-Connect: A complete failure to bond.

Partial Connect: An incomplete or faulty bond.

These nanoscale defects highlight the difficulty of achieving consistent and reliable connections in hybrid bonding.

Inspection Resolution Requirements:

The graph on the right details the resolution capabilities of various inspection technologies:

For nanoscale interconnects, Nano-CT is essential, offering resolutions below 1 μm.

For even finer inspection, tools like TEM (Transmission Electron Microscopy) and FIB (Focused Ion Beam) are required for resolutions under 0.1 μm or smaller.

Traditional techniques like Macro-CT or Micro-CT are insufficient for resolving nanoscale features.

Challenges in Testing and Metrology:

Nanoscale assembly defects and extreme interconnect density push the limits of conventional test and defect metrology methods.

Timely detection of data and issues is crucial to maintain the pace of development and ensure reliable assembly.

Hybrid Bonding Placement and CMP are the main cost drivers in the Hybrid Bonding process. Innovations like self-assembly can significantly reduce costs, especially as the number of chiplets increases. However, the process remains cost-intensive due to the high precision and defect sensitivity required in nanoscale bonding.

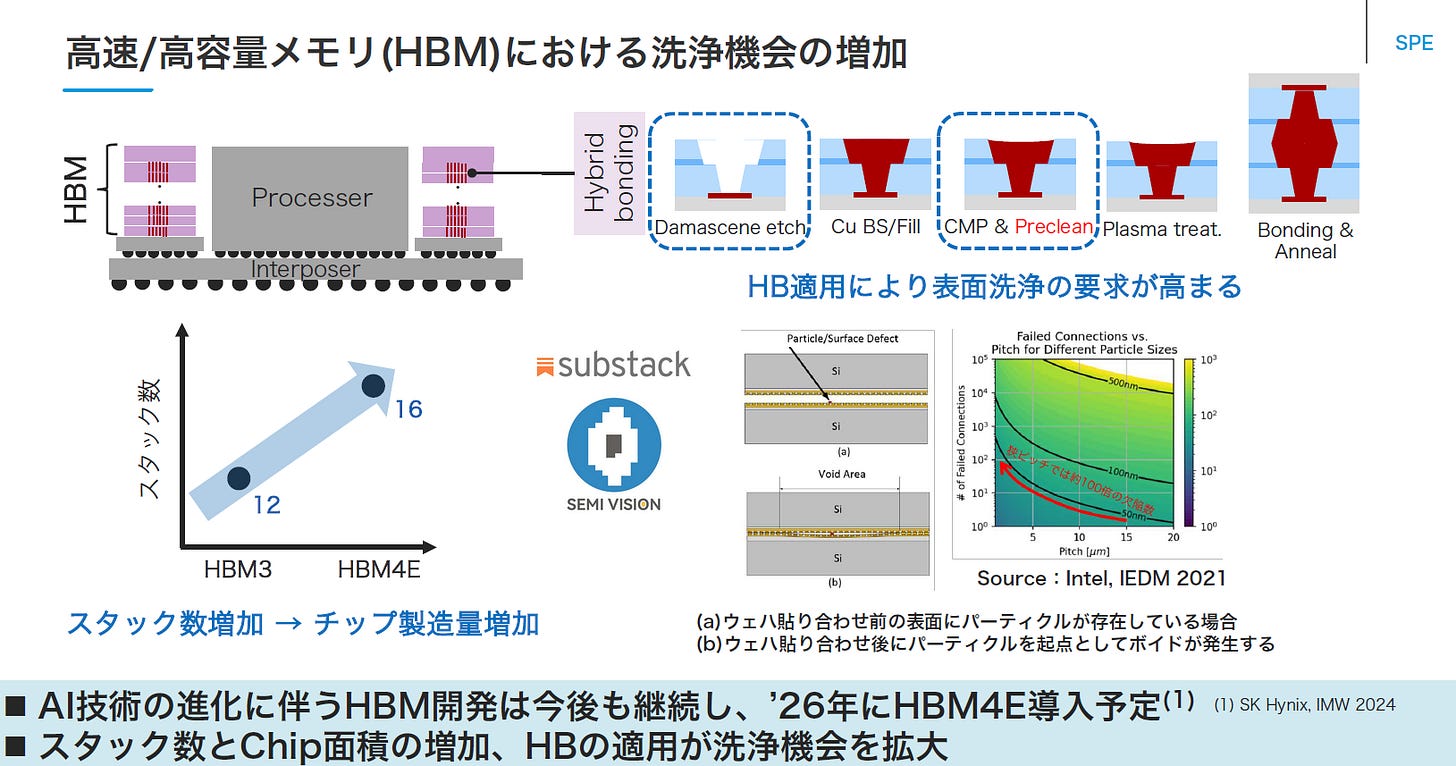

The graph from Intel (IEDM 2021) highlights:

The correlation between pitch size and defect rate due to particle contamination.

Smaller pitches are more prone to connection failures caused by surface particles, emphasizing the need for rigorous cleaning processes.

As HBM technologies evolve, the demand for cleaning processes, particularly in Hybrid Bonding, will intensify to ensure reliable connections. This is driven by the increase in stack numbers and the need to manage contamination, which becomes critical at smaller pitches and higher densities.

Challenges Yet to Overcome in Hybrid Bonding Technology

Although hybrid bonding is highly anticipated in the industry and regarded as a revolutionary technology for 3D packaging, it still faces several technical challenges. These include issues with the yield of finished bare dies and the stringent requirement for ultra-flat bonding interfaces, which pose significant challenges to the packaging process.

Additionally, the hybrid bonding process demands a cleanroom environment with an ISO 3 or higher cleanliness standard. For traditional OSAT providers, this significantly increases costs and tests their facilities and environmental control capabilities.

Nevertheless, it has become an industry consensus that chip performance improvement has shifted from relying solely on process advancements to having advanced packaging play a critical role. The increasing number of suppliers investing in the development of hybrid bonding technology will undoubtedly accelerate its progress, driving rapid advancements in chip performance.