IITC 2025 Ecosystem Spotlight: Leading Institutions and Industry Giants Shaping Interconnect Technology

Original Article by SemiVision Research ( IITC , TSMC , Samsung , SKHynix , KLA , EVG , Lam )

IEEE International Interconnect Technology Conference (IITC) 2025 to Be Held in Busan, Korea

For more detailed information on the program, please visit the official website: https://iitc2025.org/overview.php

The IEEE International Interconnect Technology Conference (IITC) 2025 will take place from June 2 to June 5 at the Westin Josun Hotel in Busan, South Korea—marking the first time this prestigious event is hosted in Korea. Organized by the IEEE Electron Devices Society, IITC is a premier global conference focusing on advanced metallization and 3D integration technologies for ultra-large-scale integration (ULSI) applications. The conference covers a wide range of topics, including Back-End-of-Line (BEOL), Middle-of-Line (MOL) interconnect design, manufacturing processes, integration challenges, reliability analysis, and emerging interconnect materials and architectures.

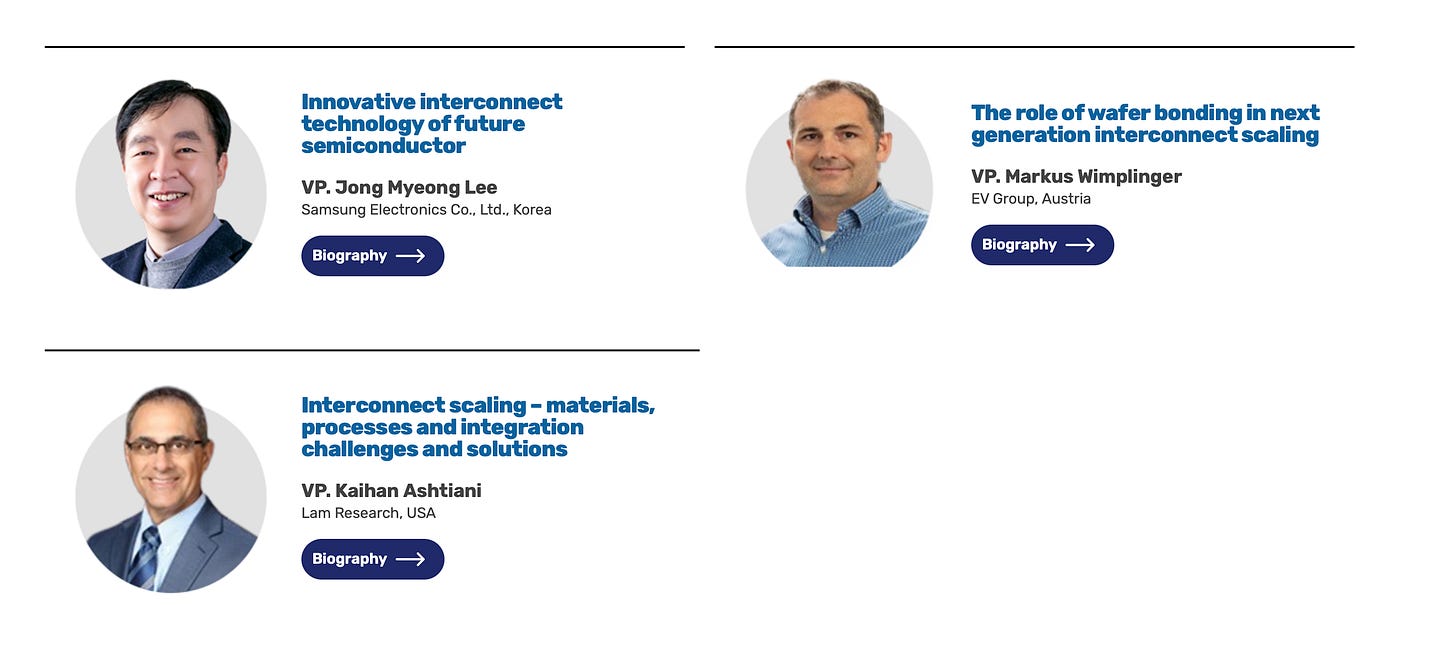

This year’s IITC 2025 will feature keynote addresses from three prominent leaders in the semiconductor industry, who will share their vision and insights on the future of interconnect technologies:

Mr. Jong Myeong Lee, Vice President at Samsung Electronics, will deliver a talk on “Innovative Interconnect Technologies for Future Semiconductor Scaling”, exploring the challenges and breakthroughs in interconnect scaling at advanced technology nodes, particularly in the context of 3nm and below.

Mr. Markus Wimplinger, Corporate Technology Development & IP Director at EV Group (Austria), will present “Wafer Bonding and Its Role in Next-Generation Interconnect Scaling”, offering an in-depth perspective on how advanced bonding technologies—such as hybrid and fusion bonding—are enabling high-density 3D integration and chiplet architectures.

Dr. Kaihan Ashtiani, Corporate Vice President at Lam Research (USA), will discuss “Interconnect Scaling: Challenges and Solutions from Materials to Integration”, highlighting the complex interplay between material innovation, process optimization, and system-level integration in enabling next-generation BEOL/MOL scaling.

In addition to the keynotes, research teams from imec (Belgium) will present several technical papers showcasing their latest work on advanced metallization schemes, electrical reliability modeling, and novel integration approaches tailored for sub-2nm technology nodes. These contributions underscore imec’s leadership in enabling scalable and reliable interconnect technologies for future logic and memory devices.

IEEE IITC 2025 is expected to bring together leading experts, researchers, and engineers from academia, industry, and R&D institutions around the world. The conference serves as a global platform for exploring emerging interconnect challenges, cross-disciplinary innovations, and collaborative opportunities that drive the future of semiconductor technology.

The IEEE International Interconnect Technology Conference (IITC) 2025 is scheduled to take place from June 2 to June 5, 2025, at the Westin Josun Hotel in Busan, South Korea. This marks the first occasion the conference is being held in Korea. Organized by the IEEE Electron Devices Society, IITC is a premier global conference focusing on advanced metallization and 3D integration technologies for ultra-large-scale integration (ULSI) applications. The conference covers a wide range of topics, including Back-End-of-Line (BEOL), Middle-of-Line (MOL)interconnect design, manufacturing processes, integration challenges, reliability analysis, and emerging interconnect materials and architectures.

The IITC Technical Committee comprises experts from leading semiconductor companies, research institutions, and academic organizations worldwide, including:

North America and Europe: Intel, IBM, GlobalFoundries, Lam Research, Applied Materials

Asia: Samsung Electronics, TSMC, SK hynix, ASE Group, Institute of Microelectronics (IME, Singapore), A*STAR

Research Institutions and Universities: imec (Belgium), Massachusetts Institute of Technology (MIT), Stanford University, The University of Tokyo, Tsinghua University

These members play pivotal roles in paper reviews, program planning, trend analysis, and session moderation, ensuring the conference maintains its academic rigor and industrial relevance.

The IITC 2025 program features a diverse array of presentations from both industry leaders and academic researchers:

Dr. Jiho Kang, SK hynix

“Semiconductor technology trends to overcome the integration limitations for future AI memory devices”

Prof. Tetsu Tanaka, Tohoku University

“Advanced 3DIC/TSV technologies for neuron-machine interface devices”

Dr. Kimin Jun, Samsung Electronics Co., Ltd.

“BSPDN: an interconnect breakthrough powered by bonding technology”

Prof. Jyehong Chen, National Yang Ming Chiao Tung University

“The future system prospects of electrical and optical interconnects and their role in AI data centers”

Prof. Yung-Jr Hung, National Sun Yat-sen University

“Platform and devices for co-packaged optics”

CTO Shu-Jen Han, Quantum Device

“Building a quantum computer - from device to system”

For more detailed information on the program, please visit the official website: https://iitc2025.org/program.php.

Unprecedented Lineup of Invited Speakers at IEEE IITC 2025 Showcases Global Leadership in Interconnect Innovation

The invited speakers at IEEE IITC 2025 reflect the cutting edge of semiconductor interconnect technologies. Experts from leading industrial R&D centers, global IDMs, foundries, and research institutes will present novel insights spanning superconducting devices, backside power delivery, wafer-level packaging, optical inspection, and advanced metallization schemes. Their participation underscores the increasing complexity and strategic importance of interconnect scaling in the AI, HPC, and quantum computing era.

Highlights from the Invited Speaker Program:

Dr. Fabrice Nemouchi (CEA-Leti, France)

Towards 300mm superconducting devices: from FDSOI transistors to gatemon qubits

Dr. Nicolas Posseme (CEA-Leti, France)

Benefit of post-etch treatment for defectivity improvement in the BEOL

Dr. Kyoung-Woo Lee (Samsung Electronics, Korea)

Integration of advanced backside power delivery network for 2nm node technology

Dr. Bettina Wehring (Fraunhofer IPMS, Germany)

Advanced XPS depth profiling analysis of metal alloys as diffusion barriers for Cu interconnects

Dr. Larissa Juschkin (KLA Corporation, USA)

High-speed optical inspection of wafers

Dr. Koichi Motoyama (IBM Research, USA)

Reliability and performance enhancement for fully subtractive Ru Topvia interconnects

Dr. Daniel C. Edelstein (IBM Research, USA)

Innovations enabling the continued extendibility of Cu and Post-Cu damascene BEOL technology

Prof. Il-Kwon Oh (Ajou University, Korea)

Unconventional reduction in resistivity of atomic scale topological semimetal of NbP and TaP

Dr. Jongmin Baek (Samsung Electronics, Korea)

Selective deposition in interconnect: enabling high-performance and scalable integration

Mr. Blake Hodges (imec, Belgium)

Optimized two metal level semi-damascene interconnects for superconducting digital logic

Dr. Giulio Marti (imec, Belgium)

Advancing pillar-based FSAV integration of Ru interconnect to enlarge the process window and enable multi-layers of high-aspect ratio

Team Leader Juheon Yang (SK hynix, Korea)

Metal interconnection of high-bandwidth memory in wafer-level packaging

This diverse and high-caliber roster ensures IEEE IITC 2025 will deliver an unparalleled platform for exploring breakthrough interconnect innovations across the entire technology stack—from quantum and AI devices to 2nm node reliability and advanced packaging integration.

For the full invited program and session details, please visit: https://iitc2025.org/program.php

Renowned Experts Lead IEEE IITC 2025 Workshop Sessions

The Workshop Speakers at IEEE IITC 2025 represent a distinguished group of thought leaders, innovators, and senior technologists from across academia and industry. Each speaker brings domain-defining expertise to the conference, highlighting the critical role of interconnect and system integration technologies in shaping the future of AI computing, photonics, memory, and quantum systems.

The featured workshop sessions reflect the diversity and depth of innovation across key semiconductor frontiers:

Prof. Yung-Jr Hung (National Sun Yat-sen University, Taiwan)

Platform and devices for co-packaged optics

→ Addressing the integration of photonic and electrical systems in next-generation data centers.

Dr. Kimin Jun (Samsung Electronics, Korea)

BSPDN: an interconnect breakthrough powered by bonding technology

→ Introducing advanced back-side power delivery enabled by high-precision wafer bonding.

Dr. Shu-Jen Han (SEEQC, USA)

Building a quantum computer – from device to system

→ Sharing holistic insights from superconducting devices to scalable quantum systems.

Dr. Jiho Kang (SK hynix, Korea)

Semiconductor technology trends to overcome the integration limitations for future AI memory devices

→ Exploring 3D stacking and advanced packaging in the context of AI-driven memory evolution.

Prof. Jyehong Chen (National Yang Ming Chiao Tung University, Taiwan)

The future system prospects of electrical and optical interconnects and their role in AI data centers

→ Examining the architectural convergence of optics and electronics in hyperscale infrastructure.

Prof. Tetsu Tanaka (Tohoku University, Japan)

Advanced 3DIC/TSV technologies for neuron-machine interface devices

→ Bridging semiconductor innovation with neural interfacing applications through 3D integration.

These workshops not only provide deep technical insight but also connect emerging device and system-level challenges with real-world industrial trajectories. From co-packaged optics to BSPDN, from quantum computing to AI memory, IEEE IITC 2025 fosters an unmatched platform for learning and exchange among the world’s foremost semiconductor visionaries.

Acknowledgment from SemiVision to IEEE IITC 2025

SemiVision sincerely thanks the IEEE International Interconnect Technology Conference (IITC) 2025 for its generous support and inclusive collaboration. We are honored to participate in this globally significant event and deeply appreciate the efforts of the organizing committee in advancing the frontier of interconnect technologies.

We would especially like to recognize the leadership of Professor Kuan-Neng Chen, who serves as the General Chair of IEEE IITC 2025. Prof. Chen is a highly respected figure in the global semiconductor community and a key academic force behind Taiwan’s rise in advanced packaging and 3D integration research.

Prof. Kuan-Neng Chen – Biography

Prof. Kuan-Neng Chen is a Chair Professor at the Department of Electronics Engineering, National Yang Ming Chiao Tung University (NYCU), Taiwan, and currently serves as Dean of the International College of Semiconductor Technology. He is also a Distinguished Visiting Professor at Tokyo Institute of Technology and a Senior Consultant at ITRI (Industrial Technology Research Institute).

Prof. Chen received his Ph.D. in Electrical and Computer Engineering and an M.S. in Materials Science from the Massachusetts Institute of Technology (MIT). He began his career at IBM T.J. Watson Research Center, and later returned to Taiwan, where he has since played a pivotal role in both academic leadership and cross-border industrial collaborations. His past roles include Principal Investigator of Taiwan’s National Microelectronics Program and Vice President for International Affairs at NYCU.

His research focuses on 3D integrated circuits (3D ICs), low-temperature bonding, wafer-level packaging, TSV, and hybrid bonding. As the founder and director of the 3DIC Lab at NYCU, Prof. Chen has published over 400 papers, authored 3 books and 7 book chapters, and holds 87 patents. His pioneering work has been recognized at top international conferences such as IEDM, VLSI Symposium, and ISSCC.

Prof. Chen has collaborated with more than 21 global companies through joint development projects and non-exclusive technology transfers, significantly contributing to industrial innovation in advanced interconnects and heterogeneous integration.

His accolades include being named IEEE Fellow, NAI Fellow, IET Fellow, IMAPS Fellow, and CIEE Fellow. He is a recipient of the IEEE EPS Outstanding Technical Achievement Award, IMAPS Technical Achievement Award, Pan Wen Yuan Foundation Outstanding Research Award, multiple Ministry of Science and Technology Outstanding Research Awards, and five IBM Invention Achievement Awards.

Prof. Chen also actively contributes to the international academic community. He has served as General Chair of IEEE IITC, Co-Chair of IEEE IPFA, and technical committee member for IEDM, IEEE 3DIC, VLSI-TSA, and IMAPS. He is a guest editor for MRS Bulletin and IEEE Transactions on CPMT, and continues to lead efforts in global semiconductor integration and advanced packaging technologies.

Prof. Chen’s philosophy is rooted in open collaboration, innovation-driven research, and a strong commitment to nurturing talent and enhancing the future of semiconductor technology through impactful research.

For more about Prof. Chen and his research team, visit: https://3dic.lab.nycu.edu.tw/about/

Local Committee

Organized by

The Korean Institute of Electrical and Electronic Material Engineers (KIEEME)

A leading Korean academic society dedicated to research in electronic materials and packaging science. KIEEME plays a vital role in promoting international collaboration and establishing technical standards for Korea’s semiconductor materials industry.

UNIST (Ulsan National Institute of Science and Technology)

One of Korea’s top research universities, UNIST is renowned for its advanced research capabilities in nanomaterials, electronic engineering, and next-generation semiconductor manufacturing processes.

Sponsored by

International Academic Organization

IEEE Electron Devices Society

One of the most influential organizations in the field of electronic devices, supporting cutting-edge research and standardization in semiconductors, transistors, interconnects, and packaging technologies.

Materials and Chemistry

BASF

A key global supplier of photoresists, etching gases, CMP slurries, and packaging adhesives. BASF enables high-performance wafer fabrication and packaging through its comprehensive material solutions.

Merck

A market leader in semiconductor materials, Merck provides EUV photoresists, precursors, cleaning chemicals, and thin film deposition materials for advanced node processing.

Mitsubishi Chemical

Specialized in high-purity chemicals, PI (polyimide) materials, encapsulation resins, and RDL (redistribution layer) materials, Mitsubishi Chemical is a major supplier for back-end and FOPLP packaging.

Tanaka Precious Metals

Supplies high-conductivity precious metals (e.g., gold balls and bonding wires) widely used in advanced packaging interconnects and sensor components.

Process Equipment & Technology

Lam Research

A top-three global semiconductor equipment provider. Lam specializes in etching, deposition, and cleaning systems across logic and memory nodes.

Tokyo Electron (TEL)

Japan’s largest semiconductor equipment company, offering core process tools for coating, developing, etching, and thin film deposition. TEL maintains close collaborations with TSMC and Samsung.

Applied Materials

The world’s largest semiconductor equipment vendor, delivering comprehensive solutions across front-end (ALD, CMP, PVD) and back-end (advanced packaging) segments.

SCREEN

A leader in wafer cleaning, pre-exposure processing, and advanced packaging equipment, contributing to high-yield semiconductor fabrication.

TES

Specializing in etching, deposition, and inspection equipment, TES supports Korean and Chinese fabs in advanced logic and memory manufacturing.

Other Equipment and Processing Providers

NCD (Nano-COEM Division)

A Korean company known for its expertise in ALD (Atomic Layer Deposition) systems, focusing on high-k material deposition for logic and DRAM technologies.

Moses Lake Industries

A U.S.-based specialty chemical provider focused on advanced cleaning and etching solutions, supporting FinFET and GAA process integration.

KOKUSAI ELECTRIC (KF-K)

A Japanese equipment manufacturer specializing in diffusion and thin film deposition (e.g., LPCVD), offering solutions for both logic and memory devices.

Memory and Wafer-Level Manufacturing

Kioxia (formerly Toshiba Memory)

A global NAND Flash leader, Kioxia is actively developing advanced packaging, UFS solutions, and 3D NAND architectures.

ASM International

A leading supplier of ALD and CVD tools for advanced logic and memory nodes. ASM plays a critical role in enabling EUV-compatible process structures.

Research and Packaging Services

ISAC Research / AMT / iF

These Korea-based R&D and service organizations support advanced packaging development, CSP/FOWLP prototyping, and heterogeneous integration testing for next-gen semiconductor applications.