TSMC Next Wave : CoPoS and its Taiwan Supply chain

Original Article by SemiVision Research (TSMC/ Nvidia/AMD)

Advanced Packaging: Taiwan’s Strategic Push in FOPLP and CoPoS

Advanced packaging is widely recognized as a critical technological pathway to extend and surpass Moore’s Law. In the face of physical limitations on chip scaling and the slowing pace of process node miniaturization, advanced packaging enables continued improvements in computing performance and energy efficiency through system-in-package (SiP), heterogeneous integration, and high-density interconnects.

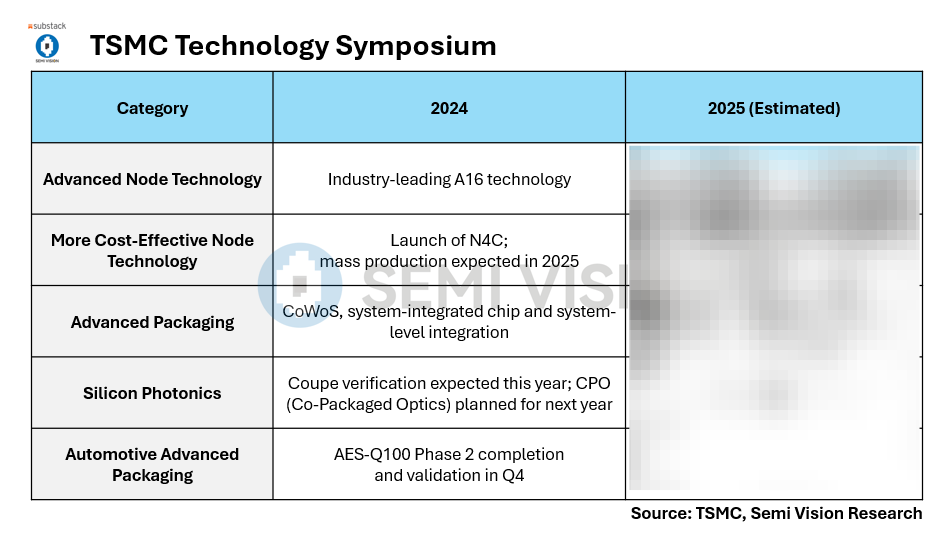

TSMC’s Technology Forum is about to take place, and according to foreign media reports, TSMC is expected to discuss the technical concept of CoPoS at the event. This will coincide with the 2025 Touch Taiwan Technology Forum, creating a synergistic effect. SemiVision Research will provide an in-depth discussion on CoPoS technology, along with an analysis of both Taiwan’s and the global supply chain landscape.

Since this packaging technology is closely related to panel-based processes, Taiwan’s panel maker Innolux has emerged as a leading company in the discussion. However, their primary focus has been on FOPLP (Fan-out Panel Level Packaging) rather than CoPoS.

FOPLP (Fan-out Panel Level Packaging) and CoPoS (Chip-on-Panel-on-Substrate) both utilize large panel substrates for packaging, but they differ significantly in architecture and application, particularly in the use of interposers. FOPLP is a packaging approach without an interposer, where chip dies are redistributed directly onto a panel substrate and interconnected through redistribution layers (RDL). This results in advantages such as lower cost, high I/O density, and flexible form factor, making it suitable for applications like edge AI, mobile devices, and mid-range ASICs where integration density is moderate.

In contrast, CoPoS incorporates an interposer, which enables higher signal integrity and stable power delivery—especially important when integrating multiple high-performance, high-power dies, such as GPU and HBM. The presence of an interposer makes CoPoS more suitable for high-end AI and HPC systems that require large-area packaging and high-speed data transmission.

Moreover, the interposer material in CoPoS is evolving from traditional silicon to glass, which offers better cost efficiency and thermal stability. Glass interposers also provide improved coefficient of thermal expansion (CTE) matching and reduced warpage, leading to higher yield and better process control for large-area integration. This is a key focus for TSMC and its supply chain partners, positioning CoPoS as a potential replacement for CoWoS-L in the future.

Previously, we discussed in depth why advanced packaging is essential, and analyzed TSMC’s strategic promotion of Chip-on-Panel-on-Substrate (CoPoS). This approach responds to increasing AI GPU packaging area demands and the production capacity constraints of CoWoS, with panel-based substrates emerging as a key enabler for future scaling and cost optimization.

Now, we turn our focus to Taiwan’s current landscape in Fan-Out Panel-Level Packaging (FOPLP) and the broader CoPoS ecosystem.

For Paid Members, SemiVision will discuss topics on

Innolux: A Leading Domestic Driver

“Panel Semiconductor”: A New Cross-Industry Concept

From HPC to Automotive Integration from FOPLP

Process Strategy and Technological Differentiation: Innolux and TSMC's Evolving Paths in Panel-Level Packaging

TSMC’s CoWoS Bottleneck and the Strategic Shift Toward CoPoS

Taiwan E-core Ecosystem (Supply chain)

Glass substrate fabrication process

TSMC CoPoS Innovation and Roadmap