The Era of Hybrid TIM Has Arrived: How Liquid Metal × Silicone is Redefining the Thermal Resistance Limits of Advanced Packaging

Original Articles By SemiVision Research (IEEE ECTC, Intel , TSMC, Nvidia, Foxconn ,Winston )

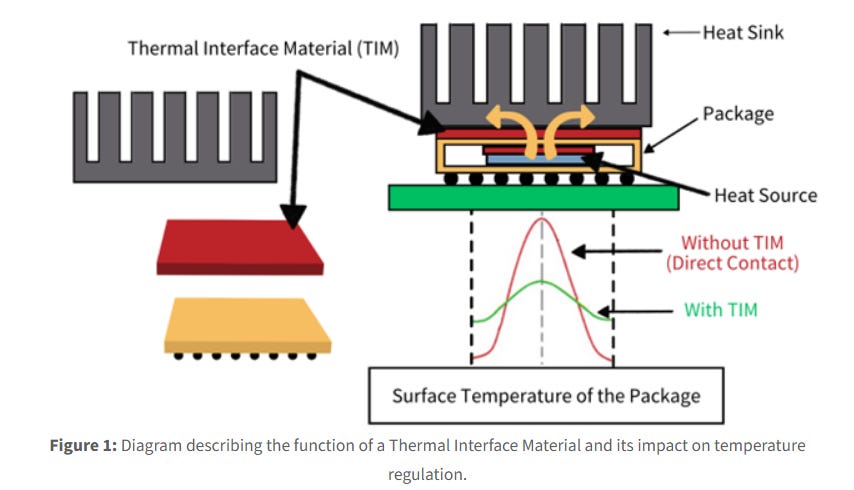

When discussing the thermal challenges of AI chips, the performance and design of Thermal Interface Materials (TIMs) directly determine thermal resistance and the efficiency of the heat conduction path. This article provides a systematic overview of the mainstream TIM classifications, their physical properties, application constraints, and the impact of structural differences and thickness (BLT) between TIM1 and TIM2 on overall thermal performance.

TIMs have evolved from being a passive supporting layer to a critical enabler for system stability in AI processors, high-performance computing (HPC), and next-generation advanced packaging. As chip power densities exceed 2 W/mm², local hot spots surge beyond 100°C, and traditional cooling solutions reach their limits, the choice and design of TIMs often become the defining factor for system performance and lifespan.

Traditionally, TIMs were classified using simple metrics like thermal conductivity, softness, or ease of application. But in today’s advanced packaging context, such definitions are no longer sufficient. It is now essential to consider not only the intrinsic thermal conductivity (κ) of the material, but also:

Bond Line Thickness (BLT) under compression,

Effective contact area with both die and lid,

Interfacial thermal resistance (Rc),

Modulus stability under thermal cycling, and

Compatibility with multiple assembly and reliability testing cycles.

In recent research from Intel, a hybrid TIM architecture was introduced—combining liquid metal at the center and conformable silicone-based adhesive TIM around the periphery. This design doesn't rely solely on raw material specs but uses thermal and mechanical co-simulation to build a self-compensating thermal interface. The liquid metal handles peak heat flux, while the low-modulus adhesive TIM accommodates warpage and unevenness. A “dam” structure is used to limit flow and stabilize BLT. This architecture significantly reduces junction-to-case thermal resistance while keeping warpage and stress levels within reliability margins. In other words, heat is no longer just dissipated—it is co-engineered into the system architecture.

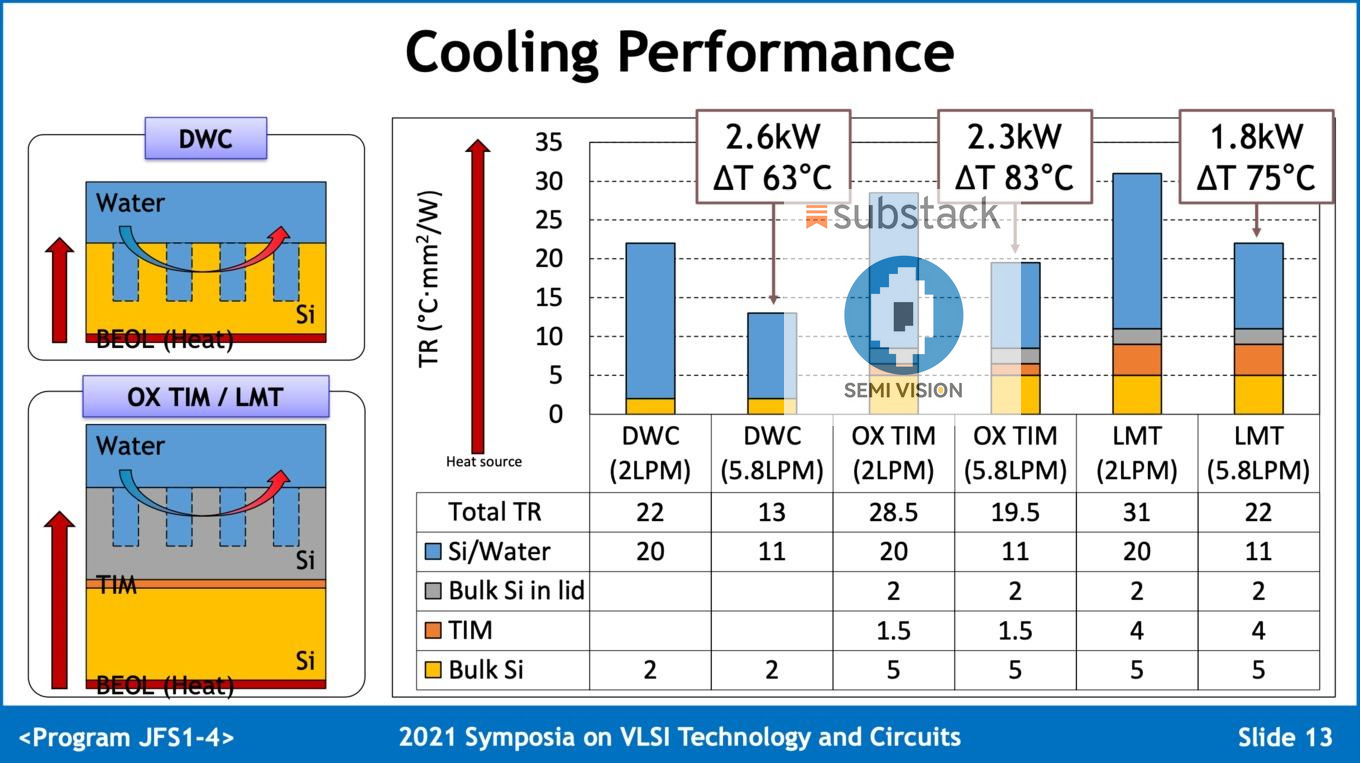

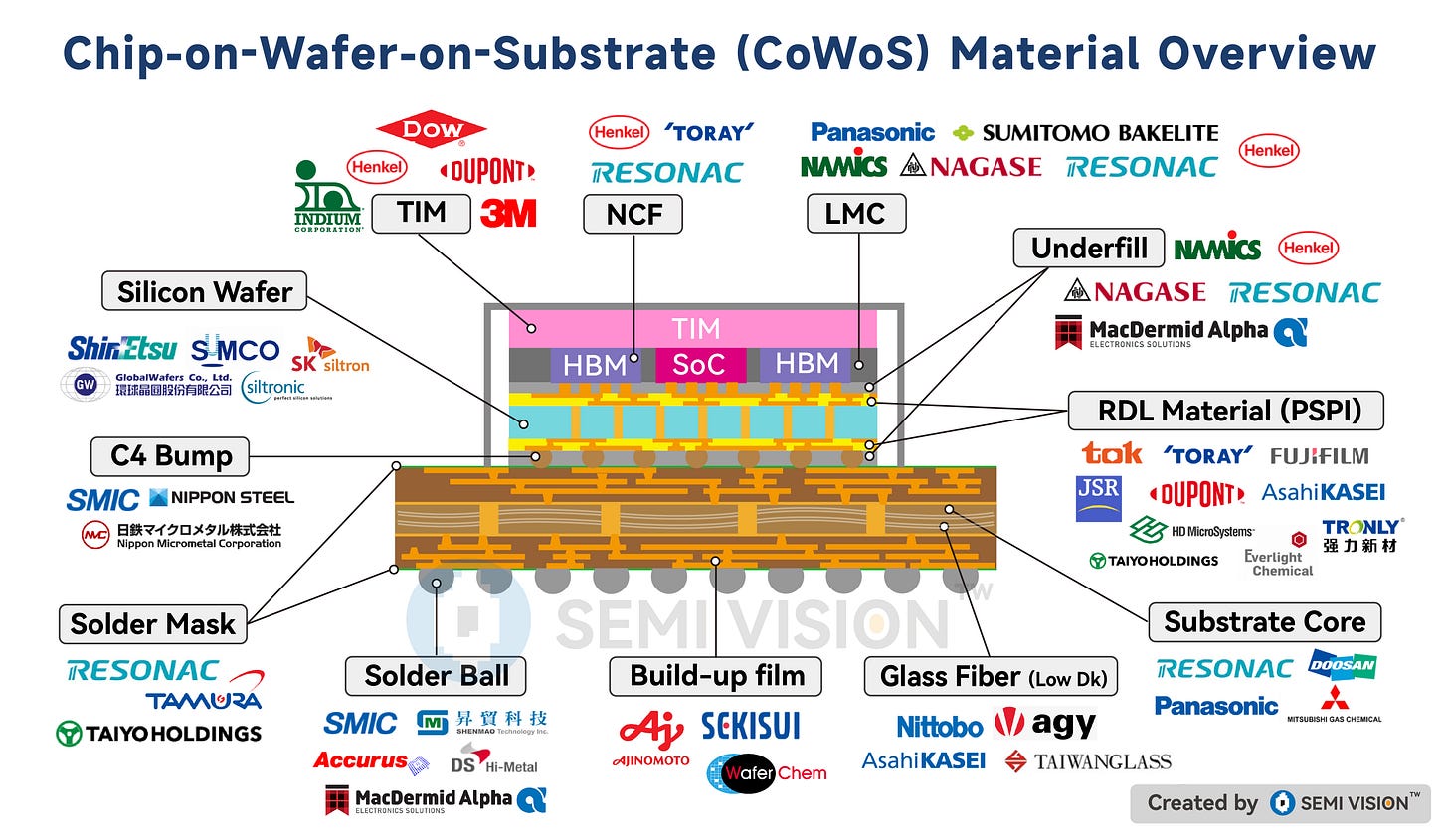

In contrast, TSMC’s mainstream approach reflects a different thermal philosophy: relying on mature polymer TIMs and process stability, while Intel pursues breakthroughs through heterogeneous material combinations and interface-level control. On platforms like CoWoS, InFO, and SoW, TSMC has implemented high-thermal-conductivity TIMs with stable TIM2-to-cold plate interfaces. However, as power density continues to climb, the question arises: Can this bottom-up cooling model scale? Or do we, like Intel, need to rethink interfacial thermal resistance from the ground up?

This leads to a deeper question:

In an era of generative AI workloads and data center power consumption exceeding hundreds to thousands of watts per server, is one good TIM material enough? Or do we need a system-level thermal interface—co-designed with the packaging platform, thermal module, and even liquid cooling system?

This is the inflection point for thermal engineering: a shift from "selecting a material" to "defining an architecture."

So, if your concern goes beyond stacking chips tighter or running cores faster, and instead focuses on how to make systems last longer within the bounds of heat and mechanical stress, then you won’t want to miss this thermal management revolution that begins with TIM.

Stay tuned for our upcoming SemiVision members-only analysis, where we dive into the next-generation directions for TIM innovation, fundamental differences in TSMC and Intel’s thermal strategies, and real-world examples of co-designed cooling-packaging architectures.

As high-performance computing (HPC) and AI accelerators continue to evolve rapidly, they are pushing power density to unprecedented levels. This trend is particularly evident in 2.5D and 3D advanced packaging architectures, where heterogeneous multi-die integration and large-area fan-out modules create complex and intensified thermal environments.

For Paid Members, SemiVision will discuss topics on

Significance of the Research From INTEL’s results

Background: Power Density & Packaging Trends

Material Rationale: Silicone-Based Liquid Metal TIM

Intel’s Solution: Hybrid TIM Structure with Mechanical Isolation

Simulation and Experimental Results From INTEL

Classification and Characteristics of TIM Materials

TIM1 vs. TIM2: Design Considerations and Thickness Implications

Technology Trends in TIM

Deep Dive into Thermal Interface Materials: Key Mechanisms and Optimization Strategies Behind Thermal Conductivity

Thermal Conductivity: The Fundamental Metric of Heat Transfer Performance

Thermal Resistance: The Key Metric for Real-World Thermal Performance

Practical Strategies for Optimizing Total Thermal Resistance

Fundamental Composition and Mathematical Relationship of Thermal Resistance

Physical Causes and Key Factors of Contact Resistance

Strategies for Reducing Total Thermal Resistance (R_TIM)

Thermal Conductivity ≠ Cooling Performance: The Need for System-Level Co-Design

Application Scenarios and Future Outlook

Liquid Metal TIM: Advantages and Challenges in AI/HPC and Advanced 2.5D/3D Packaging

Thermal Management Architecture and Functional Roles

Application Scenarios and Corresponding Thermal Solutions

Toward Co-Design, Modularity, and System-Level Thermal Optimization

Additive Cold Plate Revolution: Fabric8Labs’ Breakthrough in High-Performance Chip Cooling