2025 TSMC North America Technology Symposium_Topics Discussion_Part4

Original Articles by SemiVision Research

At the 2025 TSMC North America Technology Symposium, one of the most closely followed topics was TSMC’s progress in silicon photonics. This year, TSMC introduced several new concepts and updates in this area.

For Paid Members, SemiVision will provide an exclusive analysis, focusing in particular on TSMC’s updated architectural diagram for CoWoS, which now includes new elements relevant to its silicon photonics integration roadmap.

Much of this information was also referenced in TSMC’s 2024 academic and technical conferences. Here, we revisit and consolidate those technical insights to give members a clearer view of TSMC’s silicon photonics development pace and trajectory.

For Paid Members , SemiVision discuss topics on

A Deep Dive into TSMC’s Silicon Photonics Strategy

SemiVision will provide in-depth commentary for paid members, covering the following key areas:

COUPE Technology Details:

Examining its role in Co-Packaged Optics (CPO) and how it enhances data transmission efficiency through tighter photonic-electronic integration.

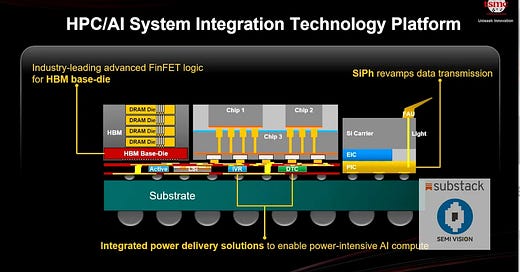

CoWoS Packaging Evolution:

Analyzing the design challenges and technical solutions related to TSMC’s 9.5-reticle CoWoS platform, which supports ultra-large chip integration.

Integration of Silicon Photonics with SoIC-X:

Evaluating the implications of hybrid bonding between PIC and EIC on future AI and HPC system architectures.

These insights are designed to help members gain a deeper understanding of TSMC’s strategic positioning in silicon photonics, and how it will shape the next generation of advanced computing platforms.

Latest Developments in CoWoS Architecture and Silicon Photonics Integration

Key Challenges in Optical Engine Integration

TSMC’s Strategic Silicon Photonics Platforms: Building the Foundation for Next-Generation Optical Integration

COUPE 2.0 (Compact Universal Photonic Engine)

iOIS (Integrated Optical Interconnect System)

EPIC-BOE (Electronic-Photonic Integrated Chiplet for Broadband Optical Engine)

Building a Scalable Silicon Photonics Ecosystem

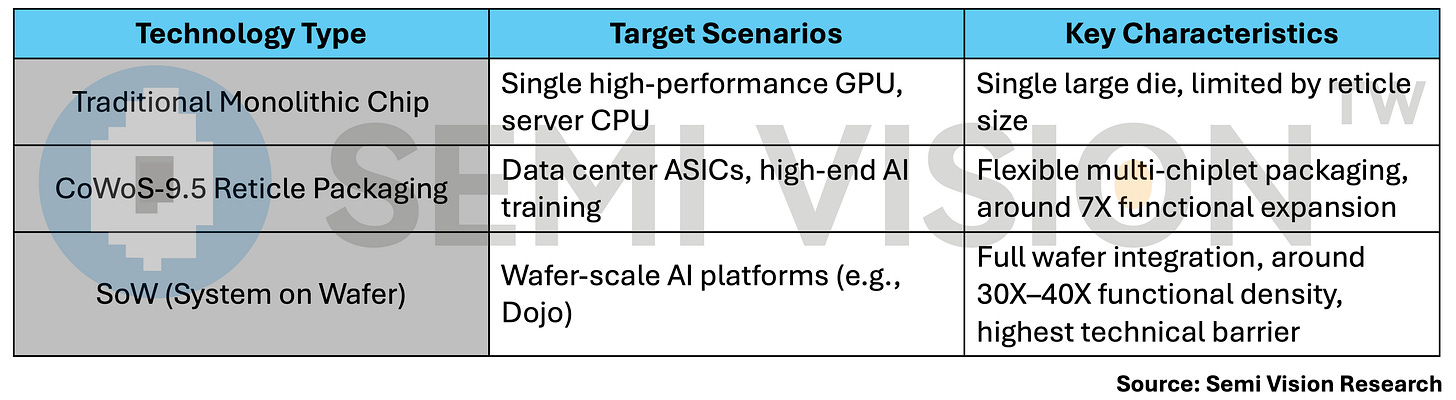

Rethinking Memory Wall Challenges in the Era of CoWoS-9.5

SoW-X: Extending the CoWoS-L Concept to the Wafer Scale

Why Compute Efficiency Can Exceed 40X in SoW Systems

Evolution and Application of SoW (System on Wafer) Technology