Cooling is the New Architecture: TSMC’s IMC-Si and the Future of AI Packaging

Original Articles By SemiVision Research (IEEE ECTC , IEEE VLSI , TSMC)

Thermal Bottlenecks in the AI and HPC Era: Cooling Becomes the New Compute Enabler

As AI and high-performance computing (HPC) continue to evolve at breakneck speed, the computational capabilities of modern chips are scaling to unprecedented levels. However, the real bottleneck in this race is no longer process node scaling or transistor density—it is thermal management.

With the power consumption of a single AI chip now reaching several hundred to even over a thousand watts, traditional air cooling and indirect liquid cooling solutions are no longer sufficient. Cooling is rapidly shifting from a secondary design concern to a central determinant of system architecture feasibility and energy efficiency.

The future of scalable compute infrastructure will increasingly hinge on our ability to innovate across advanced packaging, materials, microstructural design, and direct cooling techniques.

As such, cooling solutions that move closer to the heat source, along with integrated thermal structures and process-level optimizations, are becoming indispensable to sustaining the growth of AI infrastructure. In this new paradigm, thermal engineering is not an afterthought—it’s a critical enabler of the next compute revolution.

Current Thermal Stack and the Rise of Microfluidic Cooling

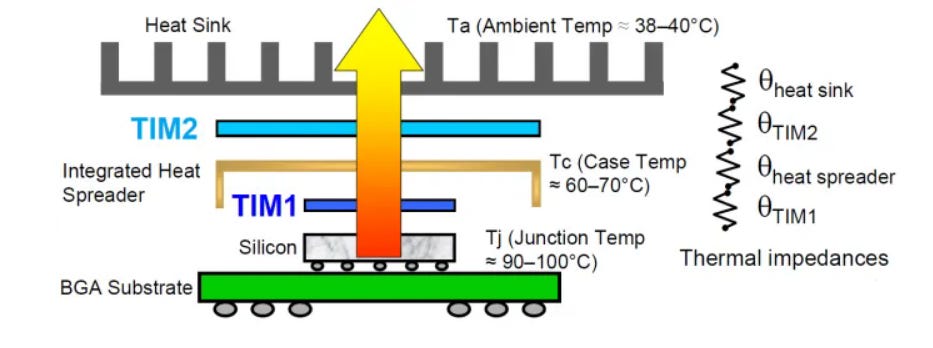

The most common thermal stack in today’s industry consists of:

AI chip + TIM1 + Lid + TIM2 + Cold Plate.

Among these layers, the cold plate is the core of indirect liquid cooling solutions. Its internal architecture, material selection, thermal resistance management, and pressure drop control are all highly complex and critical to overall system performance.

To further enhance cooling efficiency, microfluidic channels have emerged as a promising next-generation solution. By routing coolant directly to areas adjacent to the chip, this method enables rapid heat exchange closer to the heat source, offering lower thermal resistance and potentially much higher cooling efficiency compared to conventional approaches.

TSMC's Direct-to-Silicon Liquid Cooling: Background and Technical Evolution

As early as the 2021 TSMC Technology Forum, TSMC publicly introduced its concept of direct liquid cooling via backside contact with the silicon chip. The proposed solution involves fabricating mesh- or stripe-shaped microchannels on a silicon wafer or Si lid using MEMS processes, and then fusion bonding the structure to the backside of the chip.

Experimental results demonstrated that this approach could support over 2600W of total power and achieve a power density of up to 4.8 W/mm². This pioneering concept laid the technical foundation for the subsequent development of Integrated Microchannel Cooling on Silicon (IMC-Si).

2024 ECTC: TSMC Unveils First Core Paper on IMC-Si Technology

At the 2024 IEEE ECTC conference, TSMC officially presented its landmark paper, “An Energy-efficient Si-integrated Micro-cooler for High Power and Power-density Computing Applications”, revealing for the first time a production-viable and energy-efficient silicon-integrated micro-cooler (IMC-Si) designed for high-performance computing.

Background and Motivation:

According to the 2023 HIR (International Roadmap for Devices and Systems), the average power density of AI/HPC chips has increased from 1.1 W/mm² in 2018 to 2.2 W/mm² in 2023, and is expected to exceed 20 W/mm² within the next decade.

Traditional cooling methods—such as air cooling, cold plates, and immersion liquid cooling—face significant limitations in efficiency, cost, integration complexity, and long-term reliability.

Technical Architecture and Highlights:

Micropillar arrays are etched directly into the backside of the silicon substrate and paired with liquid inlet/outlet (LIO) channels, enabling direct liquid cooling with no intermediate thermal interface materials (No TIM).

The elliptical cross-section micropillars are designed to minimize pressure drop and induce turbulence for improved heat transfer efficiency.

A 3×3 compartmentalized microfluidic layout enables short-path, zoned flow, optimizing cooling performance while reducing pressure loss.

The process is built on TSMC’s SoIC® Wafer-on-Wafer bonding platform, ensuring high compatibility with advanced packaging production lines.

This development marks a key milestone in addressing the thermal bottleneck of next-gen AI and HPC systems, bringing cooling technology much closer to the source of heat—at the silicon level.

2025 ECTC: Integrating Direct-to-Silicon Liquid Cooling onto CoWoS® Platform—A Step Toward Mass Production

Building upon its 2024 technical foundation, TSMC unveiled a major advancement at the 2025 IEEE ECTC with its paper titled “Direct-to-Silicon Liquid Cooling Integrated on CoWoS® Platform”. For the first time, the IMC-Si architecture was successfully integrated into the production-grade CoWoS®-R advanced packaging platform. Key highlights include:

Platform Integration:

Implemented on a 3.3X reticle-size package, simulating a highly integrated layout of 4 SoCs + 8 HBM dies.

Requires only minor modifications to existing CoWoS® process flows, demonstrating strong compatibility with established packaging lines.

Thermal Performance:

Under 10 LPM water flow at 40°C, the system achieves a thermal design power (TDP) of up to 3.4 kW (2.5 W/mm²).

Both simulation and empirical data show that micropillar structures provide ~50% higher cooling efficiency compared to non-pillar counterparts.

Warpage Tolerance Design:

Utilizes linear-dispensed sealant with high flexibility, enabling tolerance of 160–190 µm of package warpage, effectively mitigating thermal resistance increases or leakage caused by lid deformation.

Seal Reliability Testing:

Evaluated using Helium leak tests per NASA-STD-7012A. The derived water leakage threshold is 115 cc/year.

All tested samples performed well below this threshold, validating long-term seal integrity suitable for data center operation standards.

Evolution of TSMC’s IMC-Si Liquid Cooling Architecture:

2021: Concept proposal and thermal simulation introduced at TSMC Tech Forum.

2024: Thermal performance and energy efficiency of single-die configuration validated, along with process and reliability baselines.

2025: Full integration into production-scale CoWoS®-R platform, demonstrating manufacturability and performance viability in high-power applications.

Looking ahead, further refinement of micropillar geometry and hotspot-targeted cooling paths will be crucial in supporting the next generation of ultra-high-power AI chips. IMC-Si is positioned to become one of the key enabling technologies in the thermal roadmap for advanced computing systems.

In 2024, TSMC presented a paper at ECTC titled "Si-Integrated Micro-Cooler for High Power and Power Density Computing Applications." This work introduced a silicon-based liquid cooling system developed through specialized MEMS processes.

In 2025, TSMC presented a paper at ECTC titled "Direct-to-Silicon Liquid Cooling Integrated on CoWoS® Platform."

For Paid Members: SemiVision Deeply Explores the Strategic Pivot in Thermal Management for Future AI Chips

As high power density and multi-chip integration become mainstream, thermal management is no longer merely an engineering challenge but a core strategic factor shaping the evolution of AI chip architectures. SemiVision will provide an in-depth analysis and value assessment of TSMC’s IMC-Si liquid cooling solution, packaging compatibility design, and the full implementation of the NO TIMs (No Thermal Interface Materials) concept unveiled at ECTC 2025.The content will focus on the following key perspectives:

Trends in AI Chip Architecture and the Shift in Thermal Design Coupling: SoCs exceeding 1000W are becoming reality, fundamentally rewriting packaging strategies previously reliant on air cooling.

The Industry Race Behind the Learning Curve Study: TSMC and its CoWoS® ecosystem are conducting extensive experiments on process and assembly yield learning curves, exploring breakthroughs in thermal bottlenecks through micro-pillar structures, 1D sealant, and interposer-less designs.

The Engineering and Commercial Logic of NO TIMs and Direct-to-Silicon Liquid Cooling: Traditionally indispensable TIM materials are being systematically phased out under high-flow convection and IMC-Si architectures. This is not just an improvement in thermal resistance but a complete redefinition of packaging philosophy.

Frontline Insights from ECTC 2025: Several key papers have clearly indicated that future packaging thermal management strategies will shift from “surface contact conduction” to “chip-level convection.” From thermal interfaces and module designs to process compatibility, everything is being reshaped.

This is not just a technological revolution but a challenge to redefine “packaging as a thermal interface.”